# SiC and GaN Based Transistor and Circuit Advances

J.W. Palmour<sup>1</sup>, J.W. Milligan<sup>1</sup>, J. Henning<sup>1</sup>, S.T. Allen<sup>1</sup>, A.Ward<sup>1</sup>, P. Parikh<sup>2</sup>, R.P. Smith<sup>1</sup>, A. Saxler<sup>1</sup>, M. Moore<sup>2</sup>, and Y. Wu<sup>2</sup>

<sup>1</sup>Cree, Inc., 4600 Silicon Drive, Durham, NC 27703, USA, 1-919-313-5646 <sup>2</sup>Cree Santa Barbara Technology Center, 340 Storke Road, Goleta, CA 93117, USA, 1-805-968-9460

Abstract - Significant progress has been made in the development of SiC MESFETs and MMIC power amplifiers manufactured on 3-inch high purity semi-insulating (HPSI) 4H-SiC substrates. Wide bandwidth circuits using both 10 Watt and 60 watt MESFETs are presented. These MESFETs show no degradation after RFHTOL at a baseplate of 90°C for 4000 hours. High power SiC MMIC amplifiers are shown with excellent yield and repeatability using a released foundry process. GaN HEMTs on HPSI SiC are reported with >30 W/mm RF output power density, and 10 GHz PAE of 72% is also demonstrated for lower voltage devices. Finally, a GaN HEMT operating life of over 500 hours at a  $T_J$  =160°C is also reported.

#### I. INTRODUCTION

SiC MESFETs offer significant advantages for next generation commercial and military systems. Increased power density and higher operating voltage enable higher performance, lighter weight, and wider bandwidth systems. The transition to 3-inch HPSI 4H-SiC substrates (see Figure 1) and high uniformity SiC epitaxy in late 2002 has facilitated continued improvement in both SiC MESFET performance and intrinsic device reliability [1]. In addition to providing a lower cost platform, the larger diameter substrates have also accelerated the maturation of a stable 3-inch SiC MMIC process for which commercial foundry services were initiated in mid-2003. The ability to fabricate complex, high power SiC MMICs allows another degree of freedom for systems engineers in the development of next generation radar, EW, and communication systems.

Fig. 1. 3-inch and 100mm HPSI SiC substrates

# II. SiC MESFET DEVICE PERFORMANCE

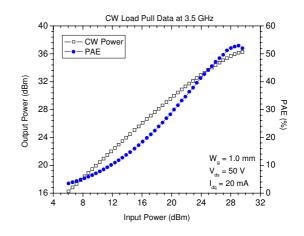

SiC MESFETs continue to mature in performance and manufacturing process stability. These devices now achieve a power density of approximately 4.0 W/mm and power added efficiencies greater than 50% on a regular basis. As an example, Figure 2 shows a 1.0 mm gate periphery MESFET operating at 50V producing 4.0 watts of output power at 66% drain efficiency (54% PAE) at 3.5 GHz.

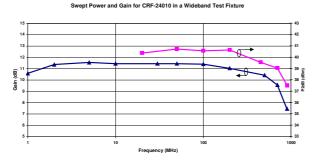

One application for which there is increasing interest in the use of SiC MESFETs is in the area of wide band military communications. New U.S. DoD programs, such as JTRS, are pushing the limits for wide bandwidth, high efficiency amplifier performance using conventional technology. The higher output impedance of SiC MESFETs facilitates matching over much broader bandwidths than are possible with silicon or GaAs transistors. As shown in Figure 3, over 10 dB of gain was achieved from 1 to 900 MHz with a standard (commercially available) 10 watt SiC packaged MESFET. No internal matching was required within the package to achieve this performance.

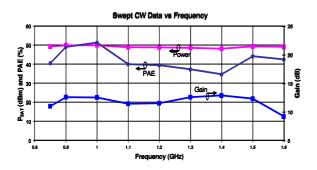

Higher power SiC MESFETs have now also become commercially available, and can likewise be used for very wide bandwidth, high efficiency amplifiers. Figure 4 shows the characteristics of a single stage amplifier based on a new 60 Watt SiC MESFET device. This device actually delivers an average of 82 watts when driven to 2.5 dB compression. This amplifier was biased

Fig. 2. On-wafer CW load pull measurement of SiC MESFET with 4.0 W/mm and 66% drain efficiency.

Fig. 3. Measured broadband performance of a prototype circuit demonstrating >10 dB of gain from 1 to 900 MHz with no internal package matching.

Fig. 4. Single stage amplifier characteristics using a 60 watt SiC MESFET device. Measured broadband performance from 0.9 to 1.5 GHz shows >12 dB of gain and average output power and PAE of 82 Watts and 42%, respectively.

at 48V, and had 12 dB gain from 0.9 to 1.5 GHz, with a high average PAE of 42%.

#### **III. SiC MESFET RELIABILITY**

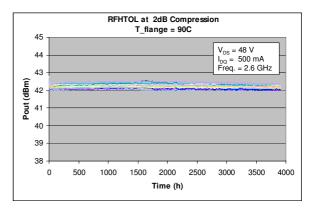

Reliability studies conducted on 10-watt SiC MESFETs fabricated on HPSI substrates demonstrate robust device characteristics. Figure 5 shows data from an high temperature operating lifetime test under RF drive (RFHTOL). The baseplate for these fifteen devices was held at the maximum rated temperature of 90°C for these parts. The parts were driven continuously at 2.6 GHz and 2 db compression, and the associated PAE was 60%. One can see that there was virtually no measurable change in RF power or gain under these conditions over a period of 4000 hours.

DC accelerated life testing has also been performed on twenty 10-Watt SiC MESFETs operating at a  $T_J=295$ °C. After 210 hours, the average reduction in saturated drain current was approximately 10%. The corresponding reduction in saturated RF output power was 1dB for half the device population under test. This MTTF of 210 hours at  $T_J=295$ °C is as good or better than that reported for GaAs devices even though the SiC devices were operated at a power density four times higher. Further improvements have been subsequently made and very significant improvements have been made on the MTTF, with the data currently being measured.

Fig. 5. RF high temperature operating life (RFHTOL) data on fifteen 10-Watt SiC MESFETs operating at the rated baseplate temperature of 90°C, showing essentially no degradation after 4000 hours.

## IV. SiC MMIC CAPABILITIES

Given the rapid progress in the technical performance and reliability of SiC device technology, the focus has shifted toward process stability, yield improvement, and higher levels of integration (i.e. SiC MMIC development) with the goal of becoming a high volume, low cost supplier of the technology. Part of this effort was to convert the process to a 3-inch line, which was completed in Jan of 2003. We have since enhanced the producibility of SiC MMICs via yield improvements.

The rapid progress in this area has also allowed Cree to offer the first wide-bandgap semiconductor MMIC foundry service. Table 1 summarizes the typical performance of the unit cell transistor available from the foundry process.

| Drain Voltage                  | 50 V    |  |  |  |  |  |  |

|--------------------------------|---------|--|--|--|--|--|--|

| Gate length                    | 0.45 µm |  |  |  |  |  |  |

| P <sub>3dB</sub> Power Density | 4 W/mm  |  |  |  |  |  |  |

| PAE at P <sub>3dB</sub>        | 50%     |  |  |  |  |  |  |

| Linear Gain at 3.5 GHz         | 12 dB   |  |  |  |  |  |  |

| TABLE I                        |         |  |  |  |  |  |  |

TYPICAL FET UNIT CELL PERFORMANCE FOR THE FOUNDRY PROCESS

The MMIC process is very similar to existing GaAs MMIC processes in that it offers thinned substrates, thinfilm resistors, high voltage MIM capacitors, spiral inductors, and through-wafer vias to accommodate FET source grounding and grounding for MMIC microstrip circuit elements. Un-thinned coplanar designs can also be fabricated. The process supports MMIC amplifier performance up to 6 GHz depending on bandwidth and gain requirements.

Figure 6 shows a DC yield map of a large, high power, SiC MMIC amplifier fabricated using the foundry process. This figure shows a threshold voltage ( $V_{th}$ ) yield of 63% while 78% of the parts tested also satisfied

|       |       |       |       |       | -11   | -10.6 | -10.6 | -10.6 | -10.4 | -10.4 |      |      |      |      |      |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|

|       |       |       |       |       | -10.6 | -10.5 | -10.6 | -10.3 |       | -10.1 |      |      |      |      |      |

|       |       | -11.2 | -11   | -10.6 | -10.5 | -10.4 | -10.3 | -10.8 | -10   | -9.9  |      | -9.8 | -10  |      |      |

|       | -11.4 | -11   | -10.7 | -10.6 | -10.4 |       | -10.3 | -10.2 | -10   | -9.8  | -9.8 | -9.6 |      |      |      |

|       |       |       | -10.6 |       |       | -10.3 | -10.2 | -10.2 | -10   | -9.8  |      | -9.4 | -9.3 | -9.6 |      |

| -11.6 |       | -10.5 | -10.5 | -10.4 | -10.3 | -10.3 | -10.2 | -10.1 | -10   |       | -9.5 | -9.3 | -9.1 | -9.2 |      |

|       | -10.6 | -10.3 | -10.2 | -10.2 | -10.1 | -10.1 | -10.2 | -9.8  | -9.7  | -9.5  | -9.3 | -9.1 | -9   | -8.9 |      |

|       |       | -10.2 | -10.1 | -10.2 |       | -9.8  | -9.7  | -9.6  | -9.6  |       | -9.3 | -9.1 | -8.9 |      |      |

|       | -10.3 | -10.1 | -10   | -9.9  | -10   | -9.7  | -9.6  | -9.4  |       | -9.2  | -9.2 | -8.9 | -8.7 | -8.7 |      |

| -11.3 | -10.5 |       | -9.9  | -9.8  | -9.6  | -9.6  | -9.4  | -9.3  | -9.2  | -9.1  | -8.9 | -8.7 |      | -8.6 | -9.1 |

|       |       | -10   | -9.8  | -9.6  |       | -9.5  | -9.2  | -9.1  | -9.1  | -8.9  | -8.7 | -8.6 | -8.6 | -8.7 | -9.4 |

|       |       |       | -9.7  |       |       | -9.3  | -9    | -9    | -9    | -8.8  |      | -8.5 | -8.7 | -8.9 |      |

|       |       |       |       |       | -9.2  | -9.1  | -8.9  | -8.9  |       |       | -8.7 | -8.5 | -8.8 |      |      |

|       |       |       |       | -9.5  |       | -9    | -8.9  |       | -8.8  |       |      | -8.9 | -10  |      |      |

|       |       |       |       |       | -9.5  | -9.2  | -9.1  | -9    | -9    | -9.1  |      |      |      |      |      |

|       |       |       |       |       |       |       | -10.3 | -10.3 | -10.9 |       |      |      |      |      |      |

Fig. 6. DC yield map for a large SiC MMIC power amplifier. Shaded areas are devices passing 100 V breakdown, demonstrating a 78% yield. The  $V_{th}$  yield is 63% to a 10V +/- 1.0V target.

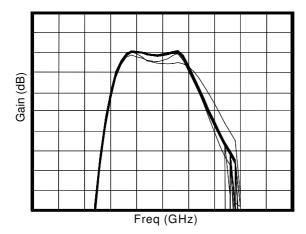

the 100 volt drain-source breakdown voltage requirement. Figure 7 shows an overlay of small signal gain for twenty-eight high power MMIC amplifiers fabricated on a 3-inch SiC substrate. The frequency and power information have been removed from the graph for proprietary reasons. It can be clearly seen, however, that the gain shape and part repeatability are indicative of a very uniform process. The two outlying gain curves were a result of physical damage to the parts during handling.

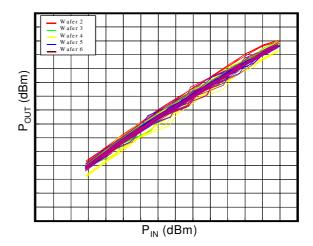

Figure 8 shows an overlay of output power versus input power for a total of eighty-six (86) high power SiC MMIC power amplifiers across a six wafer foundry lot. As seen, the power response is extremely repeatable across all 86 amplifiers and all amplifiers that passed the small signal gain requirement also passed the output power goal. The data demonstrates that the process is extremely capable of producing large numbers of high performing MMIC power amplifiers with high yields.

Fig. 7. Small signal gain of multiple high power MMICs on a single SiC wafer. Twenty-six out of twenty-eight parts met the RF gain requirement.

#### V. AlGaN/GaN HEMTs ON HPSI SiC SUBSTRATES

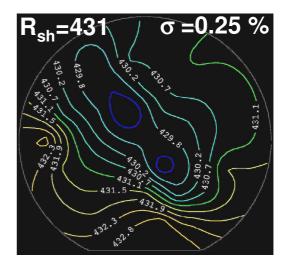

In addition to SiC MMIC technology, considerable progress is also being made in the development of Gallium Nitride-on-SiC HEMT epitaxy and devices. Figure 9 shows a sheet resistivity uniformity map demonstrating a uniformity of 0.25% across a 3-inch SiC

Fig. 8.  $P_{out}$  vs.  $P_{in}$  for 86 high power SiC MMICs across six wafers. All MMICs that met small signal gain also passed output power requirements.

Fig. 9. Sheet resistivity map for AlGaN/GaN HEMT epitaxy on 3-inch SiC showing excellent uniformity (0.25%).

wafer. The best uniformity achieved to date is 0.22% with a median value of 1.2% observed on 630 3-inch SiC wafers across multiple epi runs.

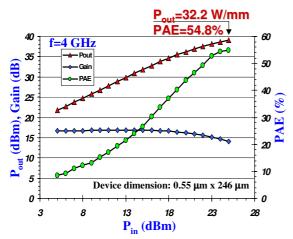

The progress in GaN epitaxy has also led to a rapid improvement in both GaN device performance and reliability characteristics over the last 24 months. GaN power densities greater than 10 W/mm have been reported for HEMTs using new epitaxial barrier layers and doped buffers. These new epi structures have also been combined with device field-plate structures to produce record power density and efficiency. Figure 10 shows a power plot of an advanced GaN HEMT incorporating an AlN barrier with an Fe-doped buffer to produce over 30 W/mm RF power density at 4 GHz, with an associated power added efficiency of 55%. These devices were operated at a drain voltage of 120 volts which is well in excess of the typical 30-40 volt operation seen in the industry.

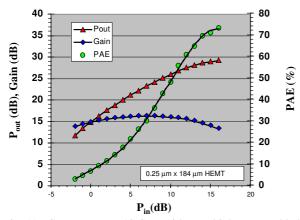

At lower, more "industry standard", drain biases, extremely high efficiencies can also be obtained from GaN HEMT devices. At the higher frequency of 10 GHz, a device with a  $0.25 \,\mu m$  gate length shows a PAE

Fig. 10. High performance GaN HEMT incorporating an AlN barrier, Fe-doped buffer, and device field-plate technology.

Fig. 11. GaN HEMT at 10 GHz with very high power added efficiency of 72% at 28 V and Class-B bias. Output power was 4.1 W/mm. The gate length was 0.25 micron

of 72% in Class B bias at  $V_{ds} = 28$  V, as shown in Figure 11. The power density at this lower bias is still much higher than is achievable in GaAs, at 4.1 W/mm, with an associated gain of 13 dB.

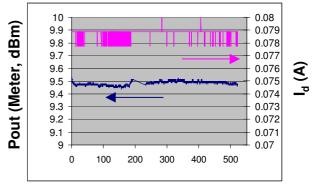

Steady improvements are also being made with regard to GaN HEMT reliability. Although considerable work remains, Figure 12 shows a plot of relative device output power and absolute drain current versus time for our best devices. As seen, there is no measurable change in either parameter over 500 hours of device operation at a junction temperature of 160°C. This part was biased at a drain voltage of 28 volts and held at 2dB RF gain compression at a frequency of 4 GHz. The room temperature P<sub>3dB</sub> RF output power density and PAE were 3.4W/mm and 66%, respectively, both before and after the applied stress.

# Time (Hours)

Fig. 12. In-situ  $P_{out}$  and  $I_{DS}$  data for a GaN HEMT at:  $V_{DS} = 28$  V,  $I_{DS} = 79$  mA,  $T_J = 160^{\circ}$ C, and  $f_o=4$  GHz. The part was held at 2 dB RF gain compression.

#### VI. CONCLUSIONS

SiC MESFETs have now been transitioned to 3-inch production capability and are commercially available in both 10 watt and 60 watt versions. The reliability of these devices appears to be excellent. SiC MMIC device yields, reliability, and processing are now sufficiently mature to support large, complex SiC MMICs on a foundry basis.

Although GaN HEMTs are known to have significant degradation issues, they are now capable of demonstrating extremely high power densities (>30 W/mm) on HPSI SiC substrates, as well as very high efficiencies (>70%) at lower biases. The degradation issues with GaN HEMTs are also showing marked improvement, with virtually no degradation observed over 500 hours at a  $T_j$  of 160°C.

#### **ACKNOWLEDGEMENTS**

The work discussed in this paper has been supported in part by contracts (N00014-C-02-0306) and (N00014-C-02-0250). Both contracts are monitored by Dr. Harry Dietrich through the Office of Naval Research.

### REFERENCES

[1] J.W. Milligan, S.T. Allen, J.J. Sumakeris, A.R. Powell, J.R. Jenny, and J.W. Palmour, "Transition of High Power SiC MESFETs from 2-inch to 3-inch Production for Improved Cost and Producibility", GaAs MANTECH Conference Digest of Papers, Scottsdale Az. (2003).